FNX6809 Manuals: Difference between revisions

| Line 92: | Line 92: | ||

<nowiki>*</nowiki> system powers off. | <nowiki>*</nowiki> system powers off. | ||

'''NOTE:''' If you are writing an | '''NOTE:''' If you are writing an OS-9 program, use <code>F$MapBlk</code> and <code>F$ClrBlk</code> instead of directly accessing these addresses. NitrOS-9 keeps track of each process' MMU LUT (but only if you use <code>F$MapBlk</code> and <code>F$ClrBlk</code>). Addressing the MMU directly can create unpredictable results. | ||

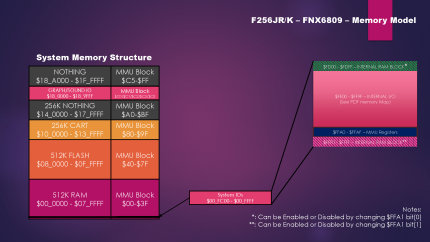

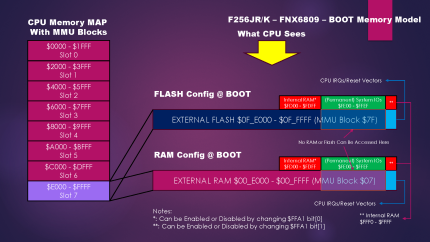

== Memory Map == | == Memory Map == | ||

Revision as of 15:37, 3 June 2024

MMU Registers

| Address | R/W | Name | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|

| $FFA0 | RW | MMU_MEM_CTRL | - | - | EDIT_LUT | - | - | ACT_LUT | ||

| $FFA1 | RW | MMU_IO_CTRL | - | - | - | - | - | $FFF0-$FFFF

Enable |

$FD00-$FDFF

Enable | |

There are 4 MLUTs (MMU Lookup Tables).

ACT_LUT these two bits specify which MLUT (0–3) is used to translate CPU bus address to system bus addresses.

EDIT_LUT these two bits will specify which MLUT (0 - 3) is being edited and will appear in memory addresses $FFA8-$FFAF.

These locations are defined in nitros9/defs/f256.d:

MMU_MEM_CTRL equ $FFA0

MMU_IO_CTRL equ $FFA1

MMU_SLOT_0 equ $FFA8 $0000-$1FFF

MMU_SLOT_1 equ $FFA9 $2000-$3FFF

MMU_SLOT_2 equ $FFAA $4000-$5FFF

MMU_SLOT_3 equ $FFAB $6000-$7FFF

MMU_SLOT_4 equ $FFAC $8000-$9FFF

MMU_SLOT_5 equ $FFAD $A000-$BFFF

MMU_SLOT_6 equ $FFAE $C000-$DFFF

MMU_SLOT_7 equ $FFAF $E000-$FFFF

* MMU_IO_CTRL bits

* $FFA1 has 2 bits:

* FFA1[0] =

* 1 = Enable internal RAM for segment $FD00-$FDFF.

* 0 = Disable; RAM/FLASH is accessible.

*

* FFA1[1] =

* 1 = Enable internal RAM for segment $FFF0-$FFFF

* 0 = Disable; RAM/FLASH is accessible.

* When enabled, the areas supersede RAM/flash, but will be disabled by RESET. When the system resets,

* those regions revert to RAM/flash. Also at RESET, the contents of RAM retain the old values until the

* system powers off.

NOTE: If you are writing an OS-9 program, use F$MapBlk and F$ClrBlk instead of directly accessing these addresses. NitrOS-9 keeps track of each process' MMU LUT (but only if you use F$MapBlk and F$ClrBlk). Addressing the MMU directly can create unpredictable results.

Memory Map

| MMU Block | MMU Page + Sector | CPU Space | Absolute [A20:A0] | WHAT | MMU Page |

|---|---|---|---|---|---|

| 2'b00 | 6'b000_000-6'b000_111 | $0000-$1CFF | $00_0000-$00_FCFF | RAM | MMU Page $00 to $07 |

| 2'b00 | 6'b000_111 | $1D00-$1DFF | $00_FD00-$00_FDFF | 256Byte Internal RAM (For OS9 Lvl 2) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E00-$1E1F | $00_FE00-$00_FE1F | I/O - System Control [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E20-$1E2F | $00_FE20-$00_FE2F | I/O - IRQ Controller [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E30-$1E3F | $00_FE30-$00_FE3F | I/O - TIMER [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E40-$1E4F | $00_FE40-$00_FE4F | I/O - RTC [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E50-$1E5F | $00_FE50-$00_FE5F | I/O - PS2 [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E60-$1E6F | $00_FE60-$00_FE6F | I/O - UART [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E70-$1E7F | $00_FE70-$00_FE7F | I/O - CODEC [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E80-$1E8F | $00_FE80-$00_FE8F | I/O - IEC [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1E90-$1E9F | $00_FE90-$00_FE9F | I/O - SDCARD [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1EA0-$1EAF | $00_FEA0-$00_FEAF | I/O - MOUSE Ctrl [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1EB0-$1EBF | $00_FEB0-$00_FEBF | I/O - VIA0 [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1EC0-$1EDF | $00_FEC0-$00_FEDF | I/O - DMA [32 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1EE0-$1EFF | $00_FEE0-$00_FEFF | I/O - MATH [32 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1F00-$1F3F | $00_FF00-$00_FF3F | TEXT LUT Foreground [64 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1F40-$1F7F | $00_FF40-$00_FF7F | TEXT LUT Background [64 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1F80-$1F8F | $00_FF80-$00_FF8F | I/O - SNES/NES Control [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1F90-$1F9F | $00_FF90-$00_FF9F | I/O - DIP SW [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FA0-$1FAF | $00_FFA0-$00_FFAF | MMU Control Registers [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FB0-$1FBF | $00_FFB0-$00_FFBF | I/O - VIA1 [16 Bytes] (F256K) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FC0-$1FDF | $00_FFC0-$00_FFDF | GRAPH - TinyVICKY Ctrl Reg [16 Bytes] | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FE0-$1FEF | $00_FFE0-$00_FFEF | RESERVED | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FF0-$1FF1 | $00_FFF0-$00_FFF1 | Reserved | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FF2-$1FF3 | $00_FFF2-$00_FFF3 | Vector - Software Interrupt 3 (SWI3) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FF4-$1FF5 | $00_FFF4-$00_FFF5 | Vector - Software Interrupt 2 (SWI2) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FF6-$1FF7 | $00_FFF6-$00_FFF7 | Vector - Fast Interrupt Request (FIRQ) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FF8-$1FF9 | $00_FFF8-$00_FFF9 | Vector - Interrupt Request (IRQ) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FFA-$1FFB | $00_FFFA-$00_FFFB | Vector - Software Interrupt 1 (SWI1) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FFC-$1FFD | $00_FFFC-$00_FFFD | Vector - Non-Maskable Interrupt (NMI) | Permanent MMU Page $07 |

| 2'b00 | 6'b000_111 | $1FFE-$1FFF | $00_FFFE-$00_FFFF | Vector - Reset (RESET) | Permanent MMU Page $07 |

| 2'b00 | 6'b001_000-6'b111_111 | $0000-$1FFF | $01_0000-$07_FFFF | RAM (448K) (Shared With Vicky) | MMU Page $08 to $3F |

| 2'b01 | 6'b000_000-6'b111_111 | $0000-$1FFF | $08_0000-$0F_FFFF | FLASH (512K) | MMU Page $40 to $7F |

| 2'b10 | 6'b000_000-6'b011_111 | $0000-$1FFF | $10_0000-$13_FFFF | CARTRIDGE(256K) RAM/FLASH | MMU Page $80 to $9F |

| 2'b10 | 6'b100_000-6'b111_111 | $0000-$1FFF | $14_0000-$17_FFFF | RESERVED | MMU Page $A0 to $BF |

| 2'b11 | 6'b000_000 | $0000-$03FF | $18_0000-$18_03FF | GRAPH - GAMMA B | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $0400-$07FF | $18_0400-$18_07FF | GRAPH - GAMMA G | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $0800-$0BFF | $18_0800-$18_0BFF | GRAPH - GAMMA R | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $0C00-$0FFF | $18_0C00-$18_0FFF | GRAPH - MOUSE Graphics | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1000-$10FF | $18_1000-$18_10FF | GRAPH - BITMAP Registers | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1100-$11FF | $18_1100-$18_11FF | GRAPH - TILE Registers | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1200-$12FF | $18_1200-$18_12FF | GRAPH - MISC Registers | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1300-$13FF | $18_1300-$18_13FF | GRAPH - SPRITE BANK 0 | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1400-$14FF | $18_1400-$18_14FF | GRAPH - SPRITE BANK 1 | MMU Page $C0 |

| 2'b11 | 6'b000_000 | $1500-$1FFF | $18_1500-$18_1FFF | RESERVED | MMU Page $C0 |

| 2'b11 | 6'b000_001 | $0000-$07FF | $18_2000-$18_27FF | GRAPH - FONT MEMORY | MMU Page $C1 |

| 2'b11 | 6'b000_001 | $0800-$0BFF | $18_2800-$18_2BFF | GRAPH - LUT2 | MMU Page $C1 |

| 2'b11 | 6'b000_001 | $0C00-$0FFF | $18_2C00-$18_2FFF | GRAPH - LUT3 | MMU Page $C1 |

| 2'b11 | 6'b000_001 | $1000-$13FF | $18_3000-$18_33FF | GRAPH - LUT0 | MMU Page $C1 |

| 2'b11 | 6'b000_001 | $1400-$17FF | $18_3400-$18_37FF | GRAPH - LUT1 | MMU Page $C1 |

| 2'b11 | 6'b000_001 | $1800-$1FFF | $18_3800-$18_3FFF | RESERVED | MMU Page $C1 |

| 2'b11 | 6'b000_010 | $0000-$12BF | $18_4000-$18_52BF | GRAPH - TEXT MEMORY (80x60 Max) | MMU Page $C2 |

| 2'b11 | 6'b000_010 | $12C0-$1FFF | $18_52C0-$18_5FFF | RESERVED | MMU Page $C2 |

| 2'b11 | 6'b000_011 | $0000-$12BF | $18_6000-$18_72BF | GRAPH - COLOR MEMORY (80x60 Max) | MMU Page $C3 |

| 2'b11 | 6'b000_011 | $12C0-$1FFF | $18_72C0-$18_7FFF | RESERVED | MMU Page $C3 |

| 2'b11 | 6'b000_100 | $0000-$001F | $18_8000-$18_801F | SOUND - SID LEFT | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0080-$009F | $18_8080-$18_809F | SOUND - SID MONO | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0100-$011F | $18_8100-$18_811F | SOUND - SID RIGHT | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0180 | $18_8180 | SOUND - OPL3 ADDY REG Low (F256K) | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0181 | $18_8181 | SOUND - OPL3 DATA REG (F256K) | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0182 | $18_8182 | SOUND - OPL3 ADDY REG Hi (F256K) | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0200-$0207 | $18_8200-$18_8207 | SOUND - PSG LEFT | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0208-$020F | $18_8208-$18_820F | SOUND - PSG MONO | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0210-$0217 | $18_8210-$18_8217 | SOUND - PSG RIGHT | MMU Page $C4 |

| 2'b11 | 6'b000_100 | $0218-$1FFF | $18_8218-$18_9FFF | RESERVED | MMU Page $C4 |

| 2'b11 | 6'b000_101-6'b111_111 | $0000-$1FFF | $18_A000-$1F_FFFF | NOTHINGNESS - RESERVED | MMU Page $C5-$FF |

Memory Model