FNX6809 Manuals

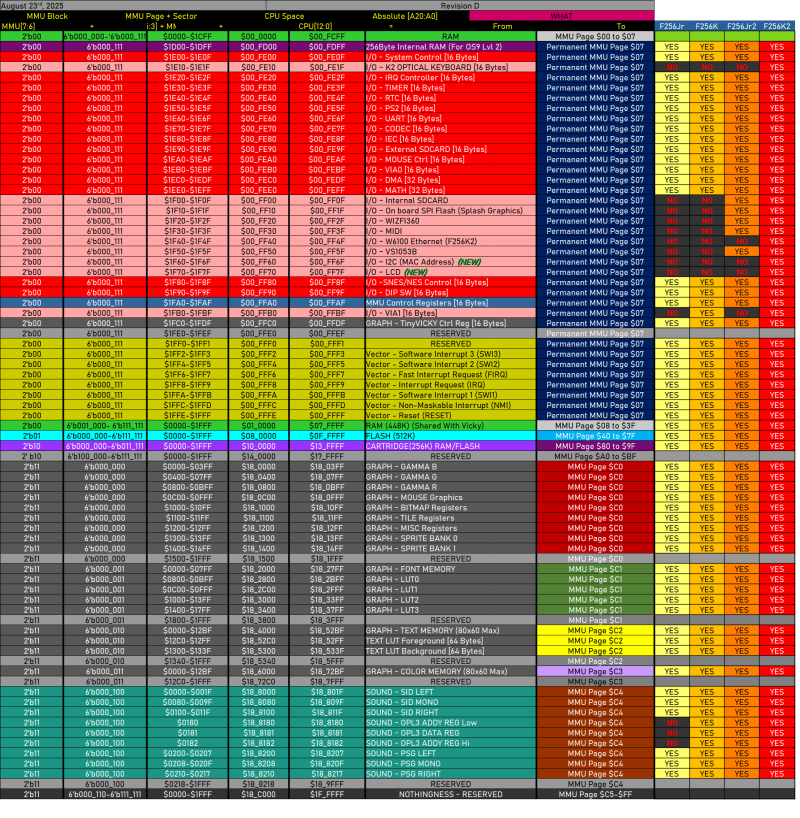

MMU Registers

| Address | R/W | Name | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|

| $FFA0 | RW | MMU_MEM_CTRL | - | - | EDIT_LUT | - | - | ACT_LUT | ||

| $FFA1 | RW | MMU_IO_CTRL | - | - | - | - | - | $FFF0-$FFFF

Enable |

$FD00-$FDFF

Enable | |

There are 4 MLUTs (MMU Lookup Tables).

ACT_LUT these two bits specify which MLUT (0–3) is used to translate CPU bus address to system bus addresses.

EDIT_LUT these two bits will specify which MLUT (0 - 3) is being edited and will appear in memory addresses $FFA8-$FFAF.

These locations are defined in nitros9/defs/f256.d:

MMU_MEM_CTRL equ $FFA0

MMU_IO_CTRL equ $FFA1

MMU_SLOT_0 equ $FFA8 $0000-$1FFF

MMU_SLOT_1 equ $FFA9 $2000-$3FFF

MMU_SLOT_2 equ $FFAA $4000-$5FFF

MMU_SLOT_3 equ $FFAB $6000-$7FFF

MMU_SLOT_4 equ $FFAC $8000-$9FFF

MMU_SLOT_5 equ $FFAD $A000-$BFFF

MMU_SLOT_6 equ $FFAE $C000-$DFFF

MMU_SLOT_7 equ $FFAF $E000-$FFFF

* MMU_IO_CTRL bits

* $FFA1 has 2 bits:

* FFA1[0] =

* 1 = Enable internal RAM for segment $FD00-$FDFF.

* 0 = Disable; RAM/FLASH is accessible.

*

* FFA1[1] =

* 1 = Enable internal RAM for segment $FFF0-$FFFF

* 0 = Disable; RAM/FLASH is accessible.

* When enabled, the areas supersede RAM/flash, but will be disabled by RESET. When the system resets,

* those regions revert to RAM/flash. Also at RESET, the contents of RAM retain the old values until the

* system powers off.

NOTE: If you are writing an OS-9 program, use F$MapBlk and F$ClrBlk instead of directly accessing these addresses. NitrOS-9 keeps track of each process' MMU LUT (but only if you use F$MapBlk and F$ClrBlk). Addressing the MMU directly can create unpredictable results.

Memory Map

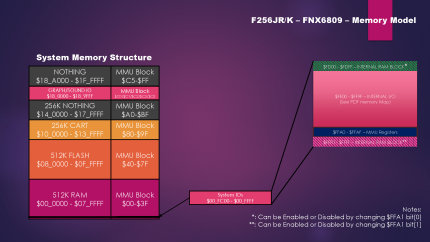

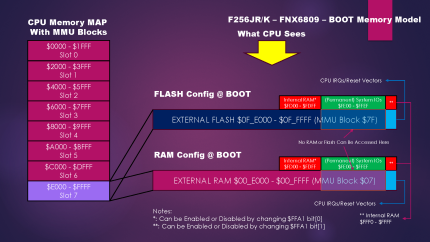

Memory Model